## Gestione delle pagine con il TLB

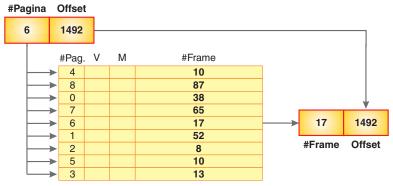

La figura seguente mostra un TLB con 9 elementi abbinata alla tabella delle pagine di un processo. Una richiesta di accesso alla pagina 6 provoca l'accesso parallelo alle righe del TLB. La riga che descrive la pagina 6 è in TLB quindi il frame corrispondente (17) può essere usato immediatamente per comporre l'indirizzo fisico e accedere alla memoria. Un tentativo di accedere a un indirizzo della pagina 13 non potrebbe invece essere soddisfatto. Per accedere alla pagina 13 la MMU deve acquisire le informazioni necessarie nella memoria e ricopiarle nel TLB. In tal caso, essendo il TLB completamente riempito, è necessario sovrascrivere una riga del TLB con i valori della tabella delle pagine della pagina 13.

TLB (Translation Lookaside Buffer)

Il seguente flowchart, che descrive la generazione dell'indirizzo fisico partendo da un indirizzo virtuale, completa il diagramma di flusso per la gestione della pagina mancante presentato nel Paragrafo 5.

## Gestione della pagina No Pagina in memoria? (V = 1) Aggiorna il TLB con i dati della nuova pagina Preleva #Frame e genera indirizzo fisico